本文为数电课程学习笔记,如有错误敬请指正

概论

研究数字电路时,通常使用符号化的电路形式对其逻辑变化进行分析。然而在涉及电路实现,即把逻辑符号变为实际电路时,则要求设计者对实现逻辑门的电路具一定了解,避免设计要求超出电路容许范围而无法实现的状况。

逻辑门分类

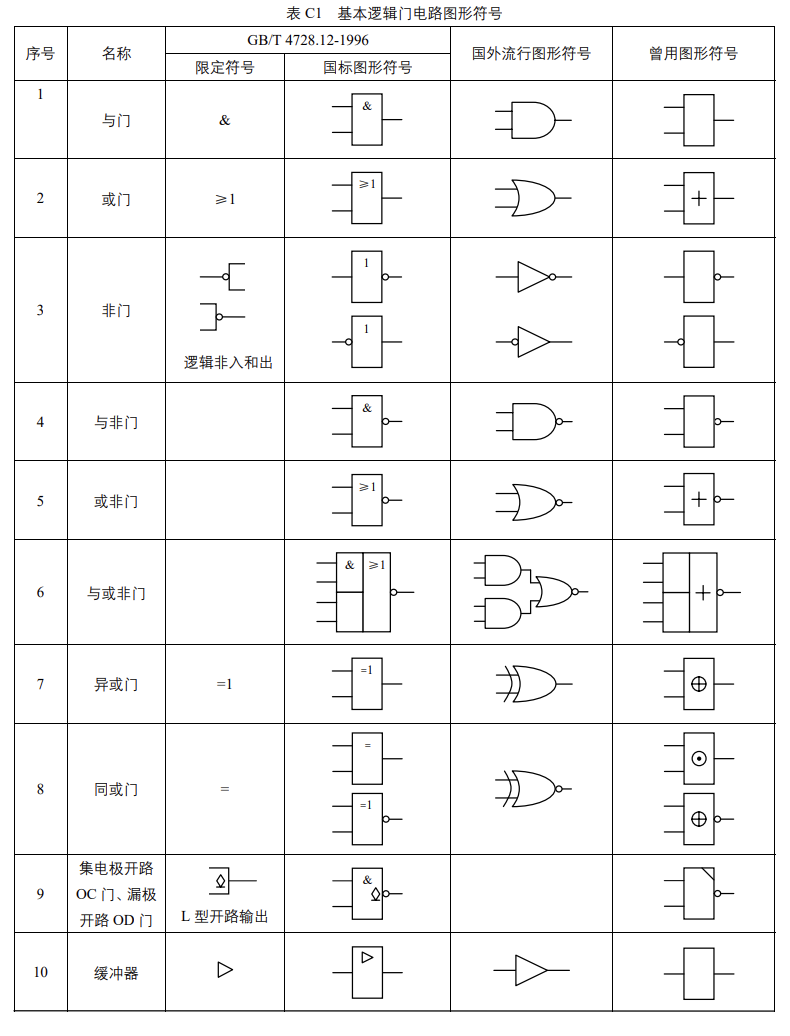

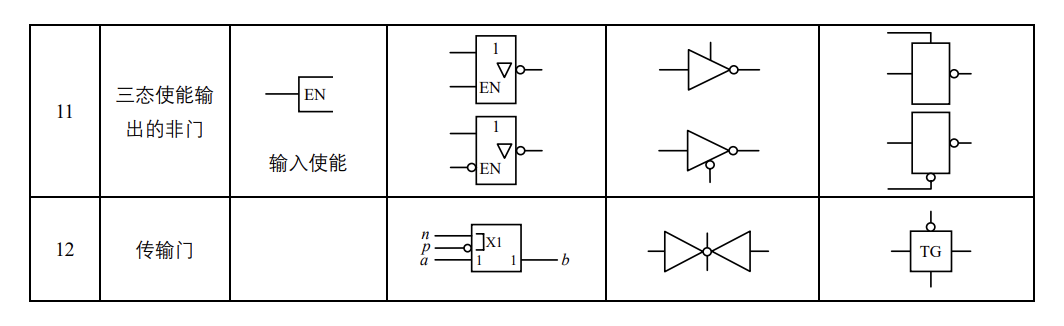

逻辑电路一般使用与非门(NAND),或非门(NOR),非门(NOT)进行逻辑实现。与门(AND),或门(OR)通过串联非门实现。缓冲器则通过2个非门串联而成。

逻辑符号

集成逻辑门分类

双极型集成逻辑门

晶体管-晶体管逻辑门电路(TTL)

单极型集成逻辑门电路

互补金属氧化物半导体逻辑门电路(CMOS)

晶体管逻辑门

器件特性

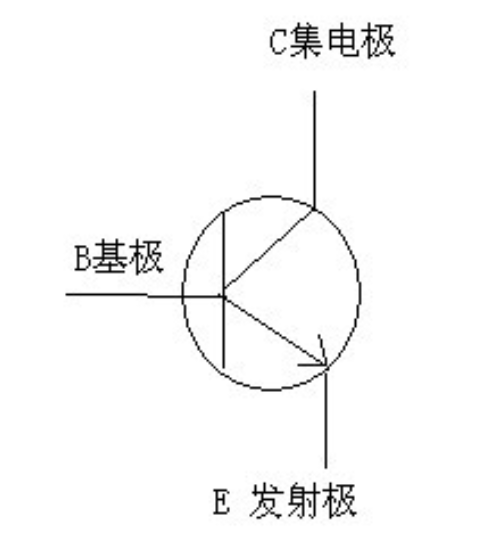

对于晶体管组成的逻辑门,我们需要先了解晶体管的电气特性。

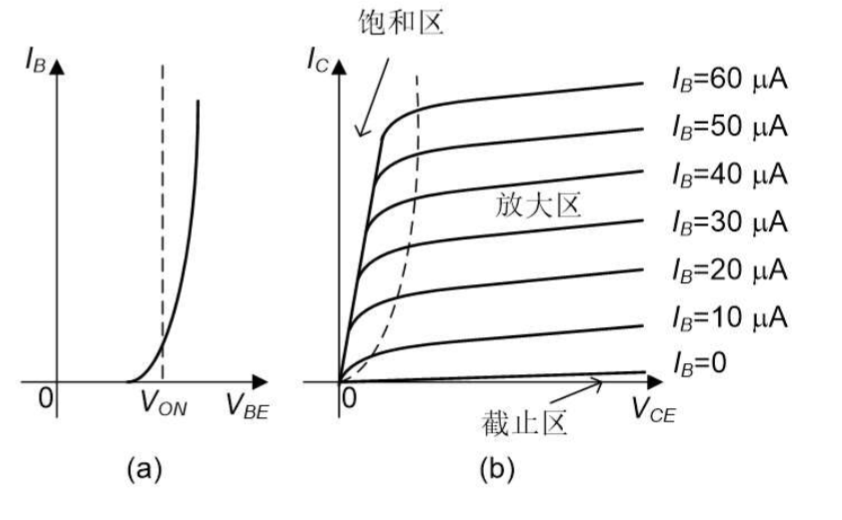

对于一个硅三极管,其输入输出特性曲线如下图所示。

一般而言,晶体管可分为三个工作区,分别对应不同的输出状态。

1)截止区:基极与射极电压差时,晶体管的双PN结反偏,仅存在极其微弱的漏电流,集电极输出电流近似为零。

2)饱和区:且时,晶体管的双PN结正偏,此时晶体管可视为一可变电阻,随增大而急剧变化。

3)放大区:且时,晶体管发射结正偏而集电结反偏,不随急剧变化,具有与间穏定的放大能力。

晶体管与非门

(待补充)

TTL与非门

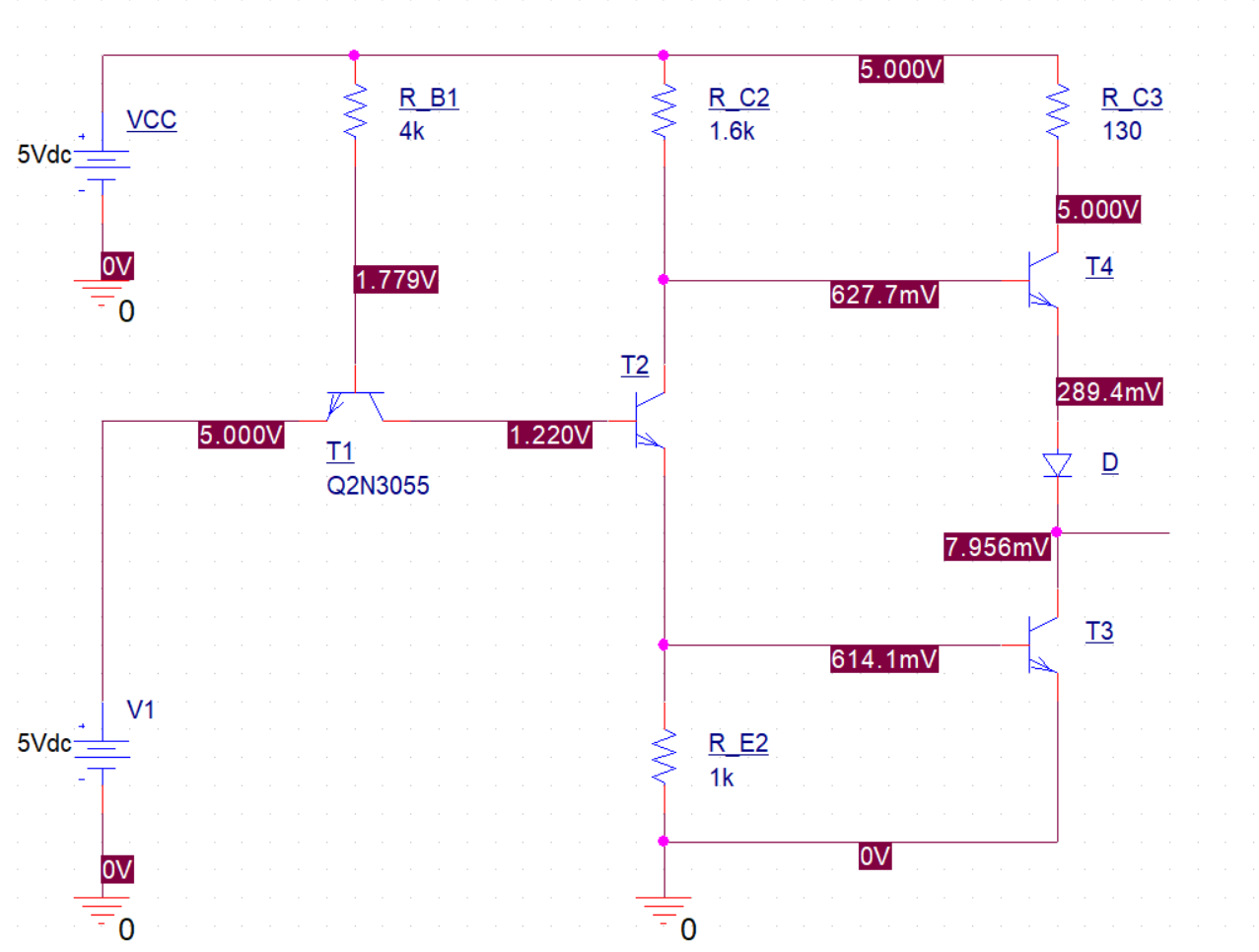

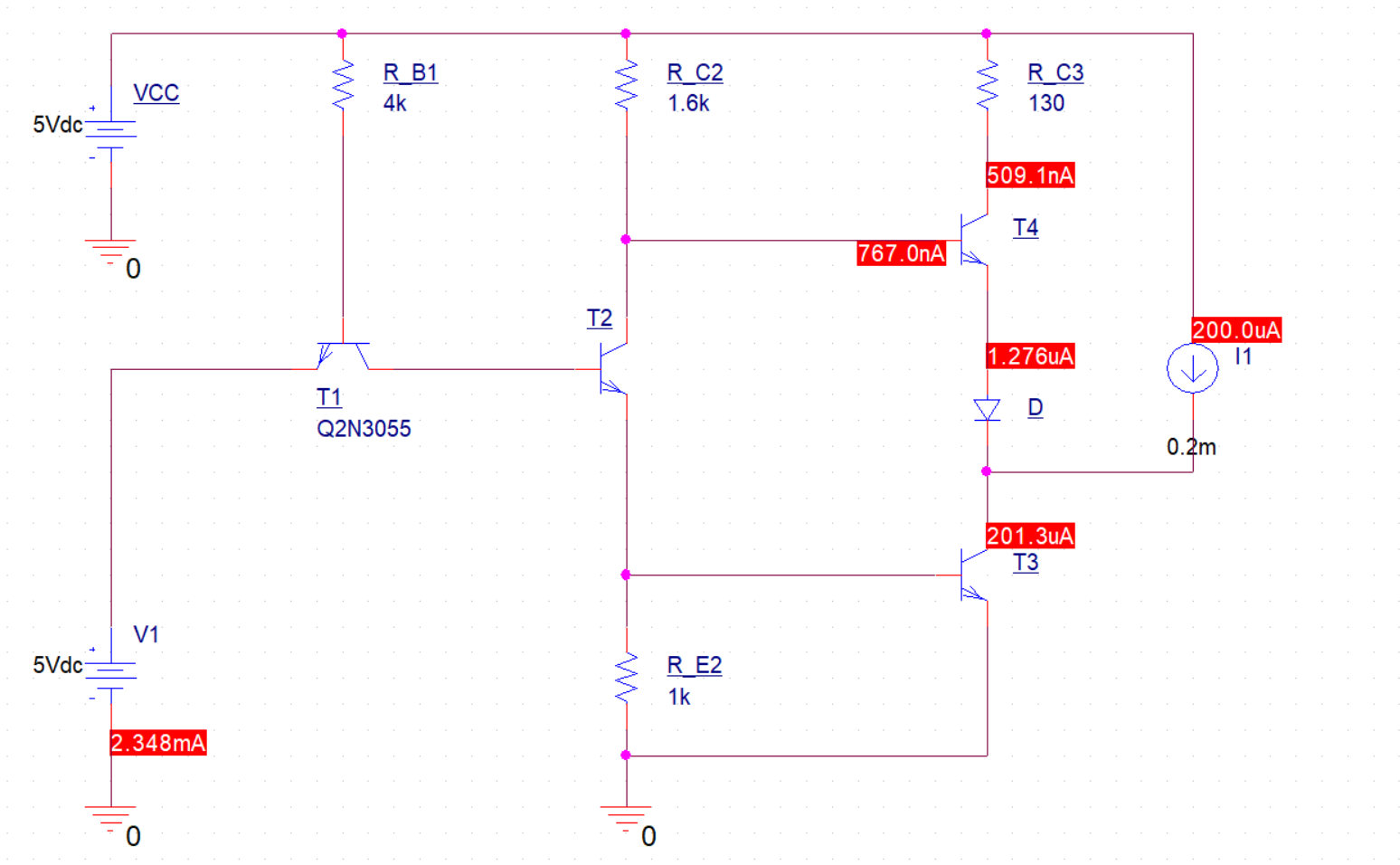

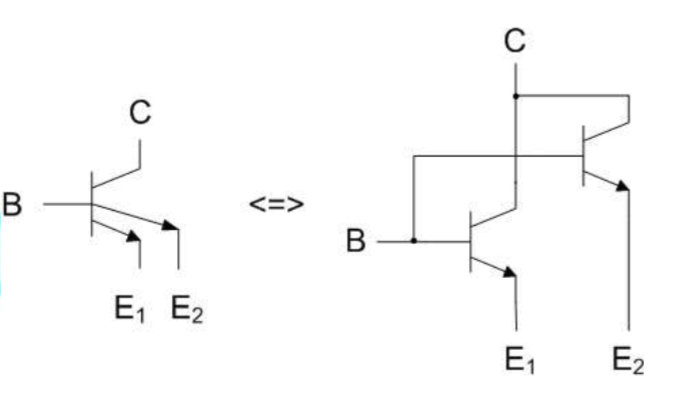

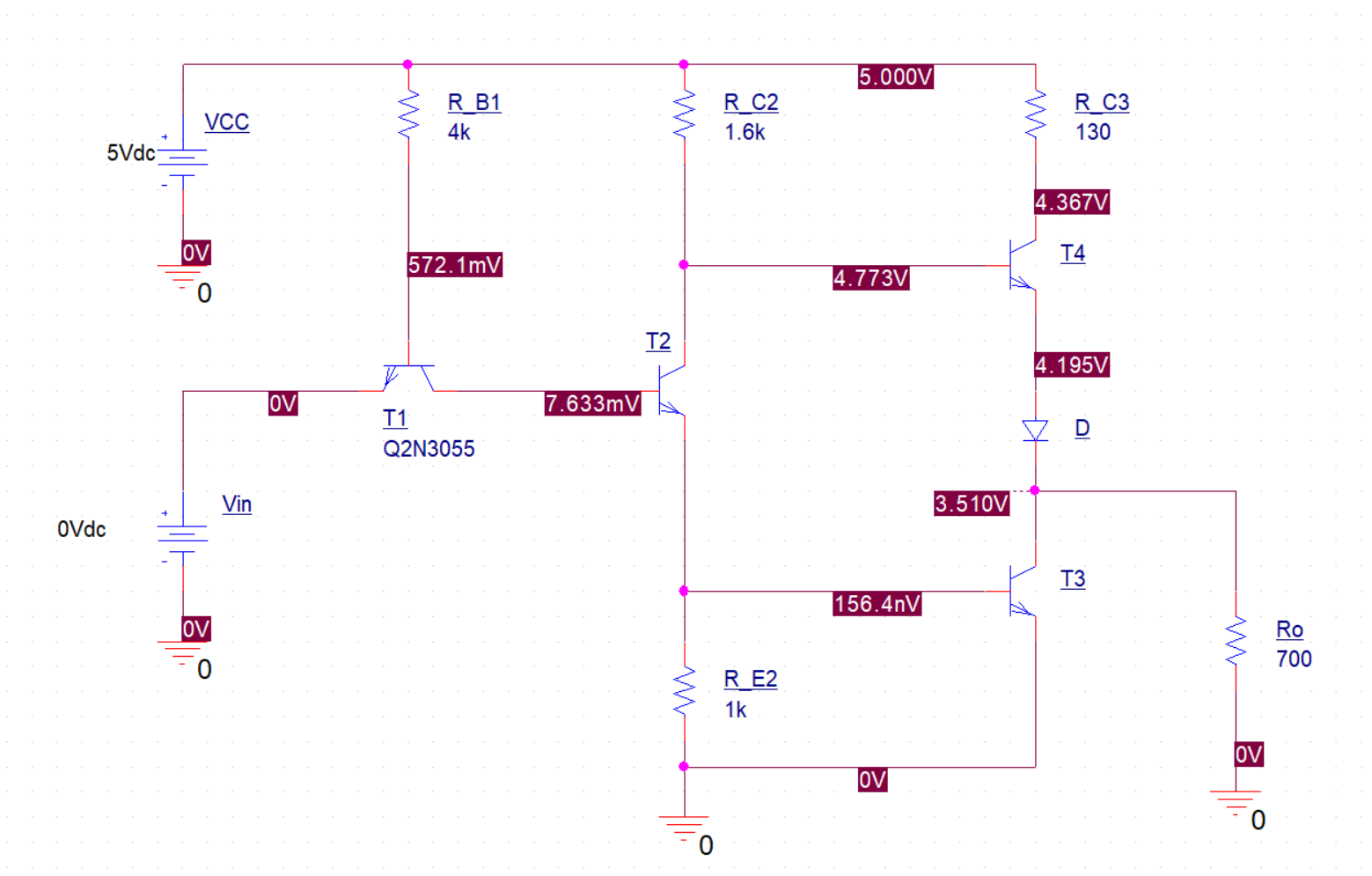

TTL与非门的电路构成如下图。

其中,T1符号代表一对共用集电极与基极的晶体管。

分析假设

分析时使用以下假设:

1)逻辑电平

输入逻辑"0"对应电压为

输入逻辑"1"对应电压为

2)导通电压

二极管及晶体管导通电压

3)电阻电压降

仅当电流流过电阻时,电阻上才存在电压降。

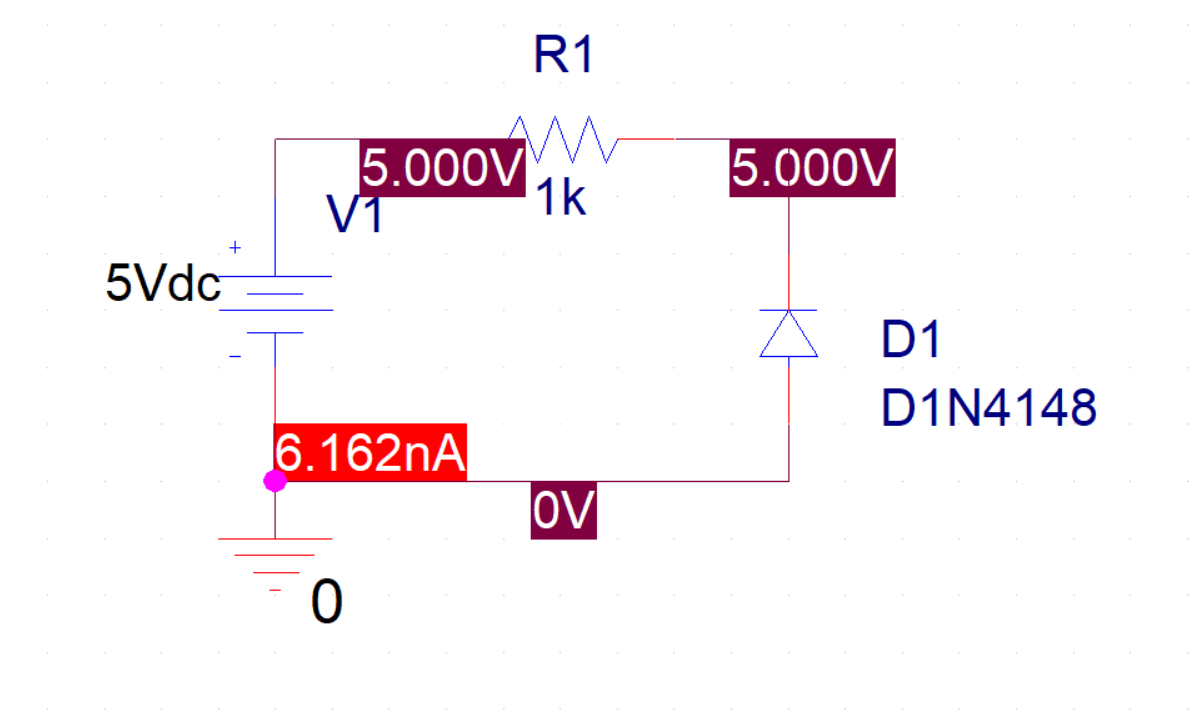

无电流时电阻俩侧的电位相同,电位差为0。电流流过电阻时,由欧姆定律及KVL定理,电阻俩侧的电势差与电阻上的电压降相等。

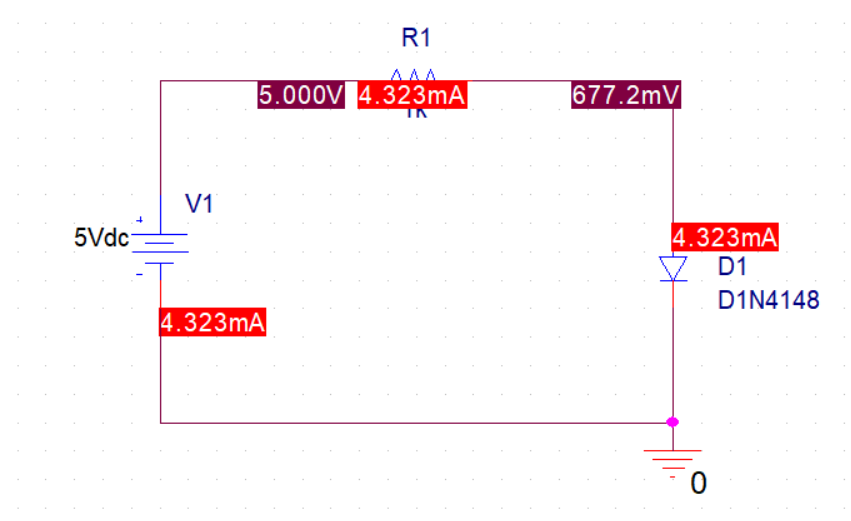

附注:此处的二极管反向截止,用于演示无电流时电阻的状态。

4)钳位作用

二极管在导通后流过电流随电压指数上升,此时二极管与串联的限流电阻进行分压,电压降主要集中于限流电阻上。二极管俩端的电压近似恒定不变且为导通电压。

附注:晶体管中PN结正偏时可视为二极管等效分析,则在极间存在钳位效应。

TTL电路分析

应用上述条件以及晶体管相关知识,可建立分析TTL电路的基本思路。

1)输入低电平(0.0-0.7V)

假设任一输入为低电平,由输入端向输出端进行分析。

首先,假设晶体管T1的发射结处于正偏状态,则由二极管钳位作用可知T1的基极电压为 0.7-1.4V,T1的极电压关系为(),则T1的发射结与集电结均为正偏状态,T1处于饱和区。此外,由于T1双正偏,基极与集电极间压降(钳位作用),

随后,分析T2晶体管状态。由于T1的基极电压为0.7-1.4V,则通过0.7V的压降后T2晶体管的基极电压为0.0-0.7V,T2晶体管处于截止状态,由于T2上近似无电流流过,则T2的发射结电压,即T3的基极电压可近似为0V,T3处于截止区。

然而,由于T2上无电流,T2的集电极电压可近似为5V,由此T4导通,经通俩个二极管的压降后输出端Y的电压为,可视为输出高电平。

此时T4处于深度饱和区,输出高电平至后级电路的输出电流由晶体管T4的集电极电流提供。

附注:仿真元件的导通电压不一定为0.7V,仅供参考。

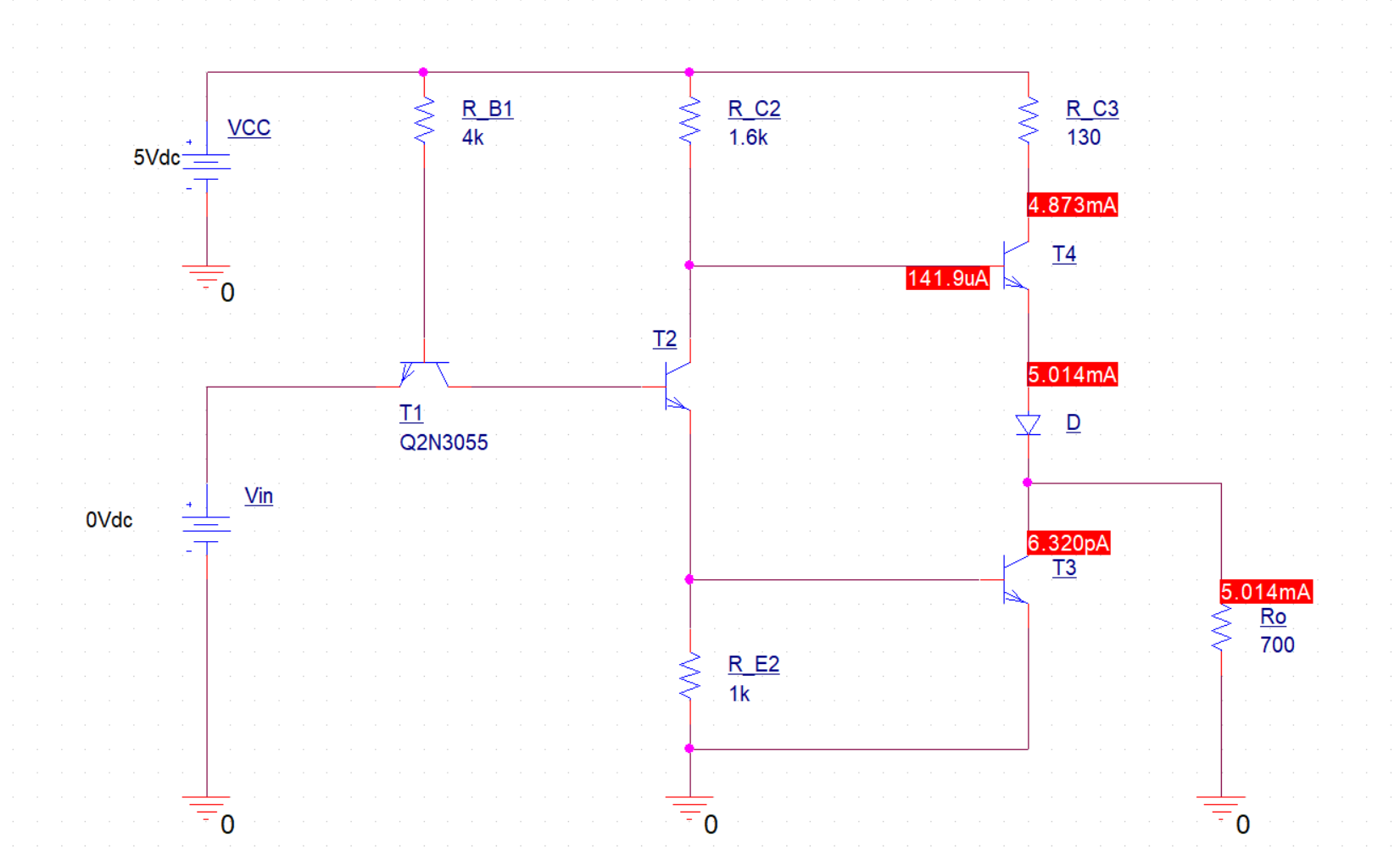

2)输入高电平(2.1-3V)

当输入为高电平时,T1的基极不再受发射极电位的钳位作用影响而受T2与T3俩个晶体管钳位,此时有,上述的三个值均由晶体管导通的钳位作用产生。

此时,T2、T3的基极电压分别为1.4V、0.7V。均大于导通电压,然而T4处于截止区(,双结反偏),因此T3集电极上不存在大电流通路,T3处于深度饱和区。

同时,由于T3处于饱和区,可等效为一电阻,在低电流下无分压,输出点近似接地,此时输出为低电平。

输出低电平时,电流从外电路流入并经过T3晶体管集电极接地,又由于(仅与T2相关)。由晶体管输出特性:决定一个与的关系函数,随集电极电流上升而增大,从而导致输出电压上升至不定态(0.7V-2.1V)影响次级电路,存在限制电路的最大允许输出电流。